- 您现在的位置:买卖IC网 > Sheet目录1214 > EVAL-ADV7403EBZ (Analog Devices Inc)BOARD EVALUATION FOR ADV7403

�� �

�

�

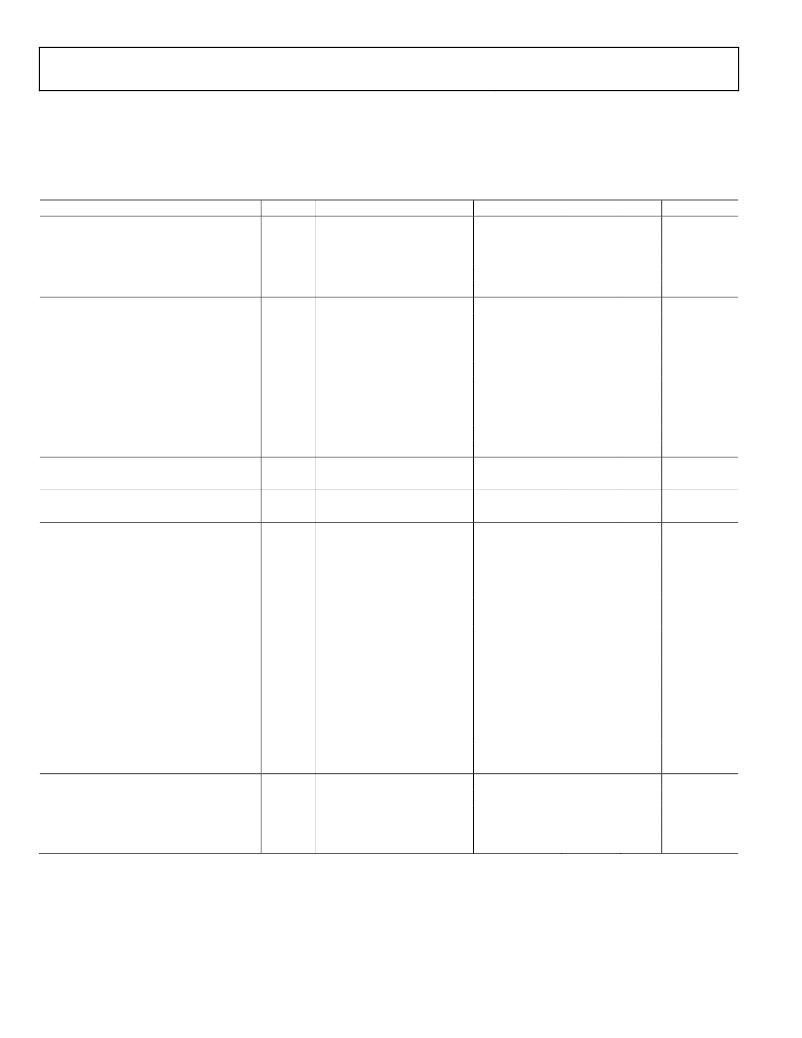

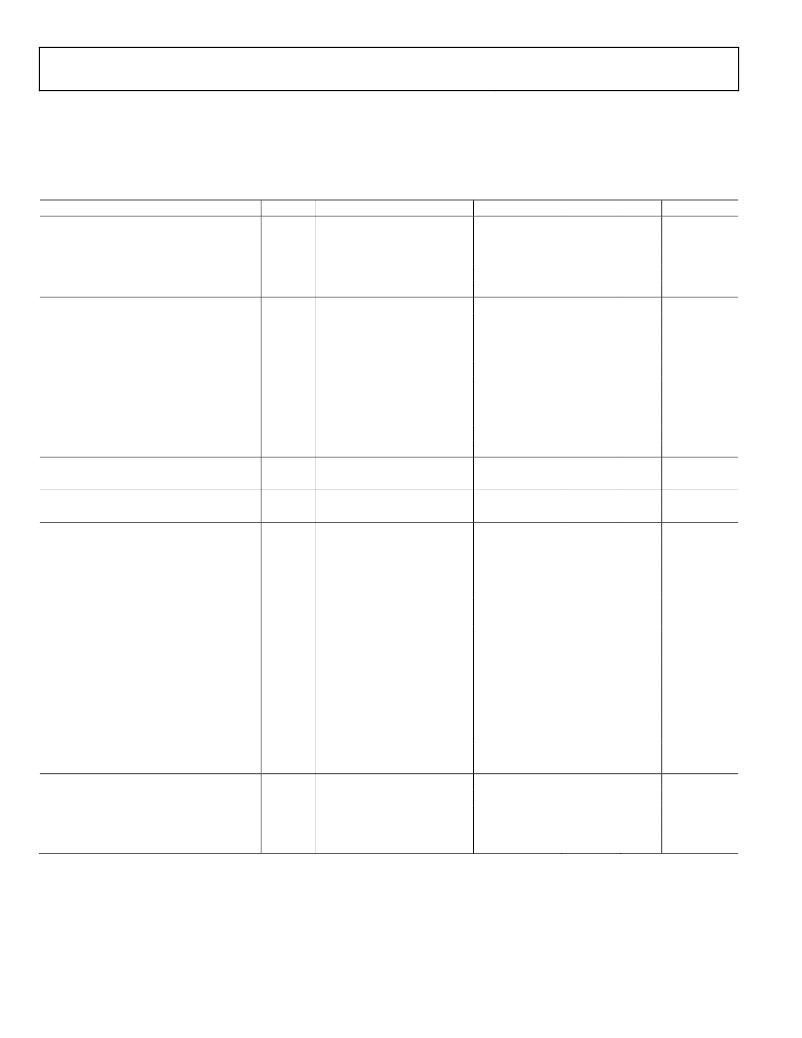

�ADV7403�

�Data� Sheet�

�TIMING� CHARACTERISTICS�

�AVDD� =� 3.15� V� to� 3.45� V,� DVDD� =� 1.65� V� to� 2.0� V,� DVDDIO� =� 3.0� V� to� 3.6� V,� PVDD� =� 1.71� V� to� 1.89� V.� Operating� temperature� range,�

�unless� otherwise� noted� is� T� MIN� to� T� MAX� :� ?40°C� to� +85°C� (0°C� to� 70°C� temperature� range� for� ADV7403� KSTZ-140).� Guaranteed� by�

�characterization.�

�Table� 3.�

�Parameter�

�Symbol�

�Test� Conditions/Comments�

�Min�

�Typ�

�Max�

�Unit�

�SYSTEM� CLOCK� AND� CRYSTAL�

�Crystal� Nominal� Frequency�

�Crystal� Frequency� Stability�

�28.63636�

�±50�

�MHz�

�ppm�

�Horizontal� Sync� Input� Frequency�

�LLC1� Frequency� Range� 1�

�14.8�

�12.825�

�110�

�140�

�kHz�

�MHz�

�I� 2� C� PORT� 2�

�SCLK� Frequency�

�400�

�kHz�

�SCLK� Minimum� Pulse� Width� High�

�SCLK� Minimum� Pulse� Width� Low�

�Hold� Time� (Start� Condition)�

�Setup� Time� (Start� Condition)�

�SDA� Setup� Time�

�SCLK� and� SDA� Rise� Time�

�SCLK� and� SDA� Fall� Time�

�Setup� Time� for� Stop� Condition�

�t� 1�

�t� 2�

�t� 3�

�t� 4�

�t� 5�

�t� 6�

�t� 7�

�t� 8�

�0.6�

�1.3�

�0.6�

�0.6�

�100�

�0.6�

�300�

�300�

�μs�

�μs�

�μs�

�μs�

�ns�

�ns�

�ns�

�μs�

�RESET� FEATURE�

�Reset� Pulse� Width�

�CLOCK� OUTPUTS�

�5�

�ms�

�LLC1� Mark� Space� Ratio�

�t� 9� :t� 10�

�45:55�

�55:45�

�%� duty� cycle�

�DATA� AND� CONTROL� OUTPUTS�

�Data� Output� Transition� Time� SDR� (SDP)� 3�

�t� 11�

�Negative� clock� edge� to� start�

�3.6�

�ns�

�of� valid� data�

�t� 12�

�End� of� valid� data� to� negative�

�2.4�

�ns�

�clock� edge�

�Data� Output� Transition� Time� SDR� (CP)� 4�

�t� 13�

�End� of� valid� data� to� negative�

�2.8�

�ns�

�clock� edge�

�t� 14�

�Negative� clock� edge� to� start�

�0.1�

�ns�

�of� valid� data�

��t� 15�

�Positive� clock� edge� to� end� of�

�?4� +� TLLC1/4�

�ns�

�valid� data�

�t� 16�

�Positive� clock� edge� to� start� of�

�0.25� +� TLLC1/4�

�ns�

�valid� data�

�t� 17�

�Negative� clock� edge� to� end�

�?2.95� +� TLLC1/4�

�ns�

�of� valid� data�

�t� 18�

�Negative� clock� edge� to� start�

�?0.5� +� TLLC1/4�

�ns�

�of� valid� data�

�DATA� and� CONTROL� INPUTS� 2�

�Input� Setup� Time� (Digital� Input� Port)�

�Input� Hold� Time� (Digital� Input� Port)�

�t� 19�

�t� 20�

�HS_IN,� VS_IN�

�DE_IN,� data� inputs�

�HS_IN,� VS_IN�

�DE_IN,� data� inputs�

�9�

�2.2�

�7�

�2�

�ns�

�ns�

�ns�

�ns�

�1�

�2�

�3�

�4�

�5�

�Maximum� LLC1� frequency� is� 110� MHz� for� ADV7403BSTZ-110.�

�TTL� input� values� are� 0� V� to� 3� V� with� rise/fall� times� ≥� 3� ns� measured� between� the� 10%� and� 90%� points.�

�SDP� timing� figures� obtained� using� default� drive� strength� value� (0xD5)� in� Subaddress� 0xF4.�

�CP� timing� figures� obtained� using� maximum� drive� strength� value� (0xFF)� in� Subaddress� 0xF4.�

�DDR� timing� specifications� dependent� on� LLC1� output� pixel� clock;� TLCC1/4� =� 9.25� ns� at� LLC1� =� 27� MHz.�

�Rev.� B� |� Page� 6� of� 20�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-ADV7510P-ABZ

BOARD EVAL FOR ADV7510

EVAL-ADV7800EB1Z

BOARD EVAL EXTERNAL DDR SD MEM

EVAL-ADV7802EB1Z

BOARD EVAL EXTERNAL DDR SD MEM

EVAL-ADV7840EB1Z

BOARD EVAL FOR ADV7840

EVAL-AVB-LISTENER

EVAL-AVB-LISTENER ADV7612

EVAL-CED1Z

BOARD EVAL CONVERTER

EVAL-CN0218-SDPZ

BOARD CFTL AD8212

EVAL-CN0229-SDPZ

EVAL-CN0229-SDPZ

相关代理商/技术参数

EVAL-ADV7441AEBZ

制造商:Analog Devices 功能描述:EVAL BOARD - Bulk

EVAL-ADV7441AFEZ_1

功能描述:视频 IC 开发工具 EVALUATION BOARD I.C. RoHS:否 制造商:Texas Instruments 产品:Evaluation Boards 类型:YPbPr to RGBHV Converters 工具用于评估:LMH1251 工作电源电压:5 V

EVAL-ADV7441AFEZ_2

制造商:AD 制造商全称:Analog Devices 功能描述:10-Bit Integrated, Multiformat SDTV/HDTV Video Decoder, RGB Graphics Digitizer, and 2:1 Multiplexed HDMI/DVI Interface

EVAL-ADV-7441A-FEZ-2

制造商:Analog Devices 功能描述:N/A - Bulk

EVAL-ADV7510-ABZ

制造商:Analog Devices 功能描述:EVALUATIOM KIT HDMI VER 1.3 TX VOM - Boxed Product (Development Kits)

EVAL-ADV7510P-ABZ

功能描述:BOARD EVAL FOR ADV7510 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:Advantiv® 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板

EVAL-ADV7510P-AKZ

制造商:Analog Devices 功能描述:EVALUATIOM KIT HDMI VER 1.3 TX - Boxed Product (Development Kits)

EVAL-ADV7511-ABZ

制造商:Analog Devices 功能描述:NEXT GEN BOARD FOR NEXT GEN HDMI TX - Boxed Product (Development Kits) 制造商:Analog Devices 功能描述:NEXt Gen Board for next gen HDMI Tx 制造商:Analog Devices 功能描述:ADV7511, HDMI TRANSMITTER, WITH ARC, EVAL BOARD; Silicon Manufacturer:Analog Devices; Silicon Core Number:ADV7511; Kit Application Type:Interface; Application Sub Type:HDMI Transmitter; Kit Contents:Board 制造商:Analog Devices 功能描述:LINEAR ICS - EVALUATION BOARD